## INTEGRATED CIRCUITS

Product specification Supersedes data of January 1995 File under Integrated Circuits, IC18 1996 Jun 27

## P8xC592

| CONTEN                                                                                      | ITS                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14                                                                                             | INTERRUPT SYSTEM                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2                                                                                      | FEATURES<br>GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              | 14.1<br>14.2<br>14.3                                                                           | Interrupt Enable and Priority Registers<br>Interrupt Vectors<br>Interrupt Priority                                                                                                                                                                                                                                                                        |

| 3                                                                                           | ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                                             | POWER REDUCTION MODES                                                                                                                                                                                                                                                                                                                                     |

| 4<br>5<br>6<br>7<br>7.1<br>7.2                                                              | BLOCK DIAGRAM<br>PINNING<br>FUNCTIONAL DESCRIPTION<br>MEMORY ORGANIZATION<br>Program Memory<br>Internal Data Memory                                                                                                                                                                                                                                                                                                                          | 15.1<br>15.2<br>15.3<br>15.4<br>16<br>17                                                       | Power Control Register (PCON)<br>CAN Sleep Mode<br>Idle Mode<br>Power-down Mode<br>OSCILLATOR CIRCUITRY<br>RESET CIRCUITRY                                                                                                                                                                                                                                |

| 7.3                                                                                         | External Data Memory                                                                                                                                                                                                                                                                                                                                                                                                                         | 17.1<br>18                                                                                     |                                                                                                                                                                                                                                                                                                                                                           |

| 8<br>9                                                                                      | I/O PORT STRUCTURE<br>PULSE WIDTH MODULATED OUTPUTS<br>(PWM)                                                                                                                                                                                                                                                                                                                                                                                 | 18<br>18.1<br>18.2                                                                             | INSTRUCTION SET<br>Addressing Modes<br>Instruction Set                                                                                                                                                                                                                                                                                                    |

| 9.1<br>9.2<br>9.3<br>10<br>10.1<br>11.1<br>11.2<br>11.3<br>12<br>13<br>13.1<br>13.2<br>13.3 | (PWM)<br>Prescaler frequency control register (PWMP)<br>Pulse Width Register 0 (PWM0)<br>Pulse Width Register 1 (PWM1)<br>ANALOG-TO-DIGITAL CONVERTER (ADC)<br>ADC Control register (ADCON)<br>TIMERS/COUNTERS<br>Timer 0 and Timer 1<br>Timer T2 Capture and Compare Logic<br>Watchdog Timer (T3)<br>SERIAL I/O PORT: SIO0 (UART)<br>SERIAL I/O PORT: SIO1 (CAN)<br>On-chip CAN-controller<br>CAN Features<br>Interface between CPU and CAN | 18.2<br>19<br>20<br>21<br>22<br>22.1<br>22.2<br>23<br>24<br>24.1<br>24.2<br>24.3<br>24.4<br>25 | Instruction Set<br>ABSOLUTE MAXIMUM RATINGS (note 1)<br>DC CHARACTERISTICS<br>AC CHARACTERISTICS<br>CAN APPLICATION INFORMATION<br>Latency time requirements<br>Connecting a P8xC592 to a bus line<br>(physical layer)<br>PACKAGE OUTLINES<br>SOLDERING<br>Introduction<br>Reflow soldering<br>Wave soldering<br>Repairing soldered joints<br>DEFINITIONS |

| 13.4<br>13.5<br>13.6                                                                        | Hardware blocks of the CAN-controller<br>Control Segment and Message Buffer<br>description<br>CAN 2.0A Protocol description                                                                                                                                                                                                                                                                                                                  | 25<br>26                                                                                       | LIFE SUPPORT APPLICATIONS                                                                                                                                                                                                                                                                                                                                 |

## P8xC592

#### **1 FEATURES**

- 80C51 central processing unit (CPU)

- 16 kbytes on-chip ROM, externally expandible to 64 kbytes

- 2 × 256 bytes on-chip RAM, externally expandible to 64 kbytes

- Two standard 16-bit timers/counters

- One additional 16-bit timer/counter coupled to four capture and three compare registers

- 10-bit ADC with 8 multiplexed analog inputs

- Two 8-bit resolution Pulse Width Modulated outputs

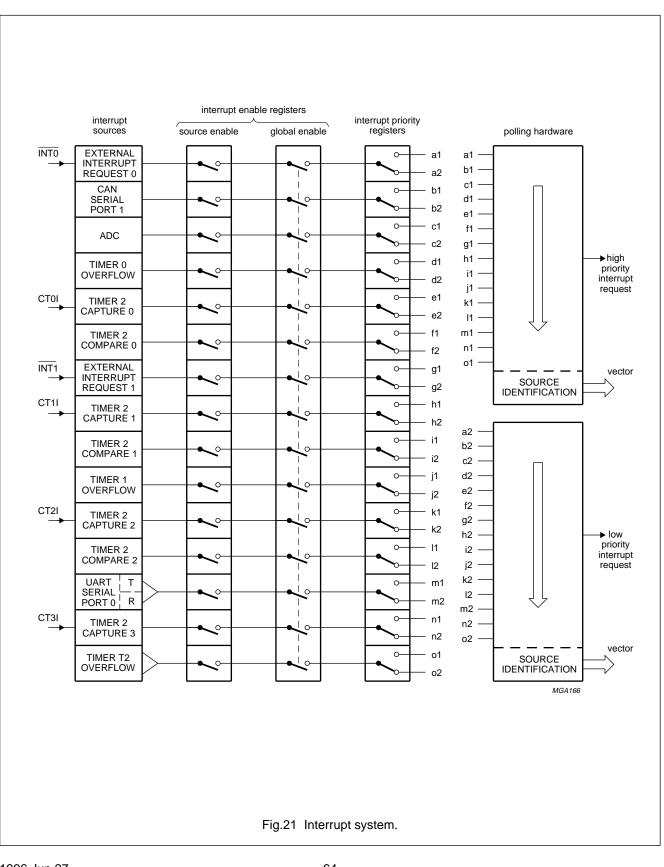

- 15 interrupt sources with 2 priority levels (2 to 6 external interrupt sources possible)

- Five 8-bit I/O ports, plus one 8-bit input port shared with analog inputs

- CAN-controller (CAN = Controller Area Network) with DMA data transfer facility to internal RAM

- 1 Mbit/s CAN-controller with bus failure management facility

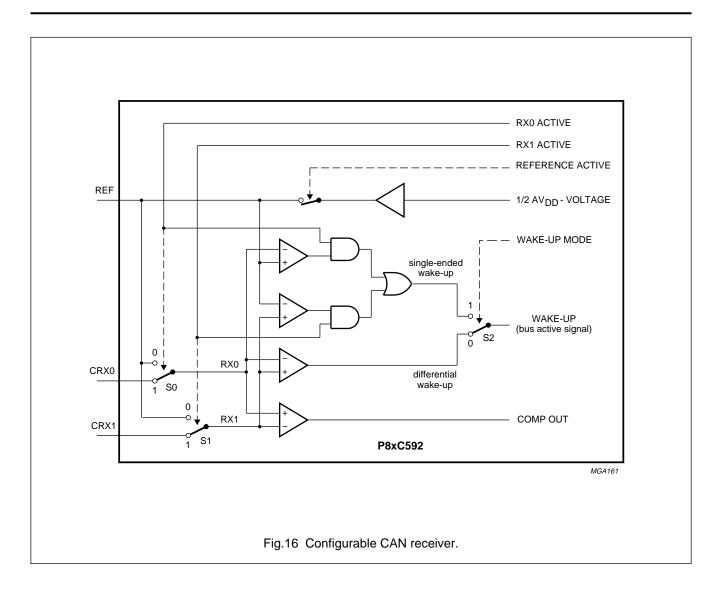

- <sup>1</sup>/<sub>2</sub>AV<sub>DD</sub> reference voltage

- Full-duplex UART compatible with the standard 80C51

- On-chip Watchdog Timer (WDT)

- 1.2 to 16 MHz clock frequency.

#### 2 GENERAL DESCRIPTION

The P8xC592 is a single-chip 8-bit high-performance microcontroller with on-chip CAN-controller, derived from the 80C51 microcontroller family.

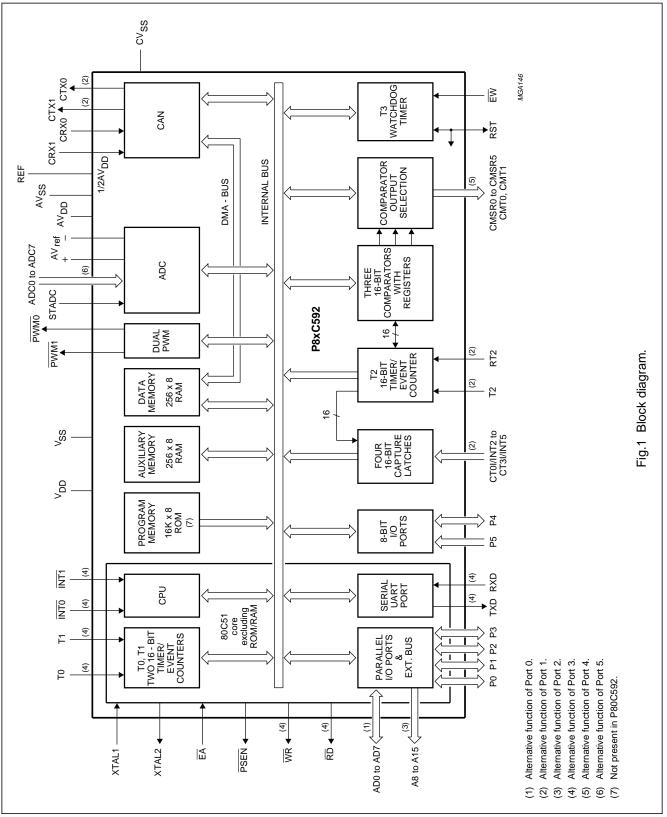

It uses the powerful 80C51 instruction set. Figure 1 shows a block diagram of the P8xC592.

The P8xC592 is manufactured in an advanced CMOS process, and is designed for use in automotive and general industrial applications. In addition to the 80C51 standard features, the device provides a number of dedicated hardware functions for these applications.

Two versions of the P8xC592 will be offered:

- P80C592 (without ROM)

- P83C592 (with ROM).

Hereafter these versions will be referred to as P8xC592.

The temperature range includes (max.  $f_{CLK} = 16$  MHz):

- -40 to +85 °C version, for general applications

- -40 to +125 °C version for automotive applications.

The P8xC592 combines the functions of the P8xC552 (microcontroller) and the PCA82C200 (Philips CAN-controller) with the following enhanced features:

- 16 kbytes Program Memory

- 2 × 256 bytes Data Memory

- DMA between CAN Transmit/Receive Buffer and internal RAM.

The main differences between P8xC592 and P8xC552 are:

- 16 kbytes programmable ROM (P8xC552 has 8 kbytes)

- Additional 256 bytes RAM

- A CAN-controller instead of the I<sup>2</sup>C-serial interface.

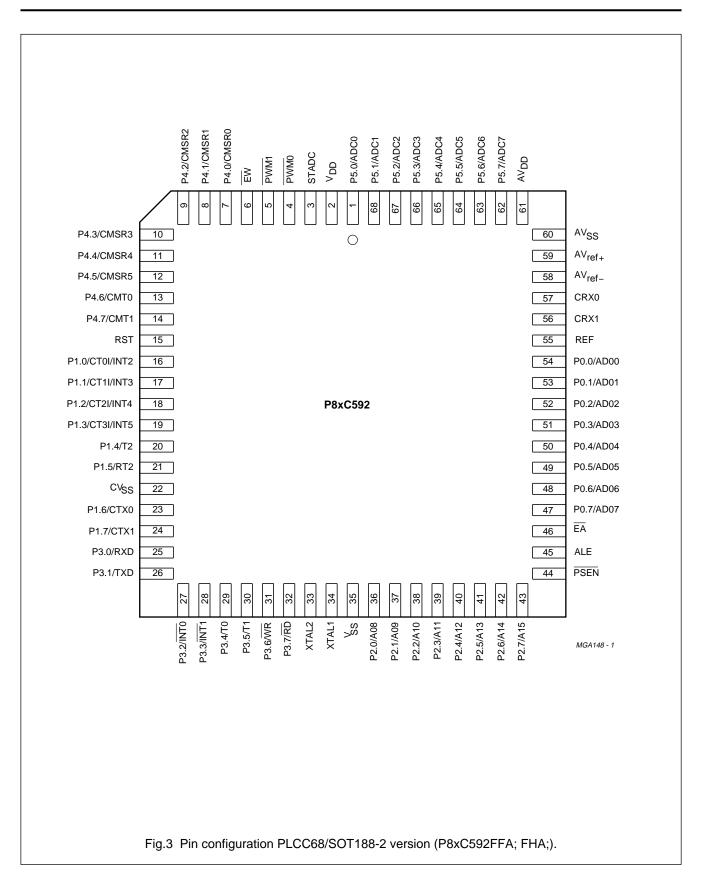

#### **3 ORDERING INFORMATION**

| ТҮРЕ        |        | PACKAGE                                      | TEMPERATURE | FREQ.<br>(MHz) |           |  |

|-------------|--------|----------------------------------------------|-------------|----------------|-----------|--|

| NUMBER      | NAME   | DESCRIPTION                                  | RANGE (°C)  |                |           |  |

| Without ROM |        |                                              |             |                |           |  |

| P80C592FFA  | PLCC68 | plactic loaded chip corrier: 69 loads        | SOT188-2    | -40 to +85     | 1.2 to 16 |  |

| P80C592FHA  | PLCC00 | plastic leaded chip carrier; 68 leads SOT188 | 501100-2    | -40 to +125    |           |  |

| With ROM    |        |                                              |             |                |           |  |

| P83C592FFA  | PLCC68 | CCC0 plantic landed ship corrier C0 lands    | SOT188-2    | -40 to +85     | 1.0 to 10 |  |

| P83C592FHA  |        | 8 plastic leaded chip carrier; 68 leads SOT  |             | -40 to +125    | 1.2 to 16 |  |

#### 4 BLOCK DIAGRAM

P8xC592

1996 Jun 27

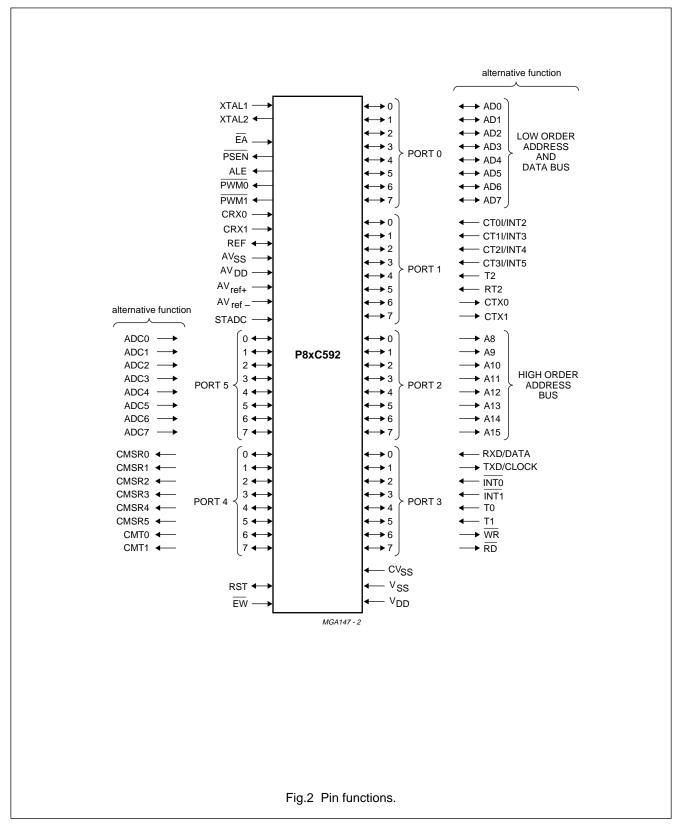

#### 5 PINNING

P8xC592

## 8-bit microcontroller with on-chip CAN

### P8xC592

Table 1

Pin description for single function pins (SOT188-2; see note 1)

| SYMBOL           | PIN | DESCRIPTION                                                                                                                                                                                                      |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>  | 2   | Power supply, digital part (+5 V). For normal operation and power reduced modes.                                                                                                                                 |

| STADC            | 3   | Start ADC operation. Input starting analog-to-digital conversion (note 2). This pin must not float.                                                                                                              |

| PWM0             | 4   | Pulse width modulation output 0.                                                                                                                                                                                 |

| PMW1             | 5   | Pulse width modulation output 1.                                                                                                                                                                                 |

| EW               | 6   | <b>Enable Watchdog Timer (WDT):</b> enable for T3 Watchdog Timer and disable Power-down mode. This pin must not float.                                                                                           |

| RST              | 15  | Reset: input to reset the P8xC592 (note 3).                                                                                                                                                                      |

| CV <sub>SS</sub> | 22  | CAN ground potential for the CAN transmitter outputs.                                                                                                                                                            |

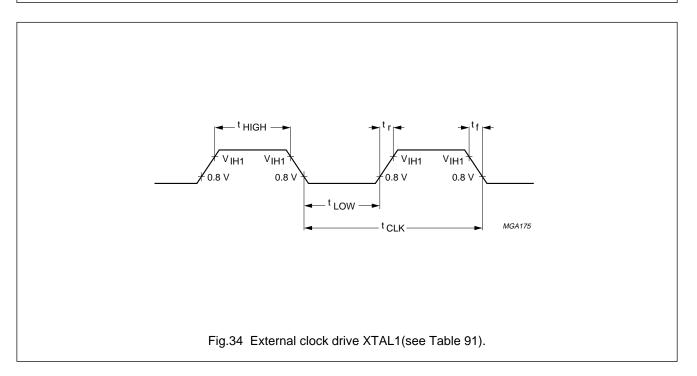

| XTAL2            | 33  | <b>Crystal pin 2:</b> output of the inverting amplifier that forms the oscillator.<br>When an external clock oscillator is used this pin is left open-circuit.                                                   |

| XTAL1            | 34  | <b>Crystal pin 1:</b> input to the inverting amplifier that forms the oscillator, and input to the internal clock generator. Receives the external clock oscillator signal, when an external oscillator is used. |

| V <sub>SS</sub>  | 35  | Ground, digital part.                                                                                                                                                                                            |

| PSEN             | 44  | <b>Program Store Enable:</b> Read strobe to external Program Memory (active LOW). Drive: 8 × LSTTL inputs.                                                                                                       |

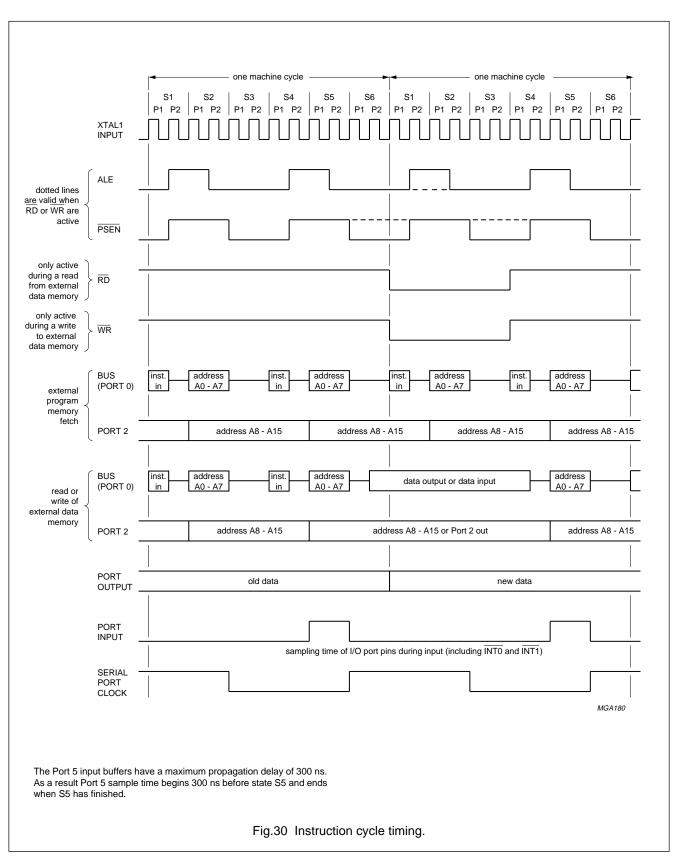

| ALE              | 45  | Address Latch Enable: latches the Low-byte of the address during accesses to external memory (note 4). Drive: 8 × LSTTL inputs; handles CMOS inputs without an external pull-up.                                 |

| ĒĀ               | 46  | External Access input. See note 5.                                                                                                                                                                               |

| REF              | 55  | <sup>1</sup> / <sub>2</sub> AV <sub>DD</sub> reference voltage output respectively input (note 6).                                                                                                               |

| CRX1             | 56  | Inputs from the CAN-bus line to the differential input comparator of the on-chip CAN-controller                                                                                                                  |

| CRX0             | 57  | (note 7).                                                                                                                                                                                                        |

| $AV_{REF-}$      | 58  | Low-end of ADC (analog-to-digital) conversion reference resistor.                                                                                                                                                |

| $AV_{REF+}$      | 59  | High-end of ADC (analog-to-digital) conversion reference resistor (note 8).                                                                                                                                      |

| AV <sub>SS</sub> | 60  | Ground, analog part. For ADC, CAN receiver and reference voltage.                                                                                                                                                |

| AV <sub>DD</sub> | 61  | Power supply, analog part (+5 V). For ADC, CAN receiver and reference voltage.                                                                                                                                   |

#### Notes

- 1. To avoid a 'latch up' effect at power-on:  $V_{SS} 0.5 V <$  'voltage on any pin at any time'  $< V_{DD} + 0.5 V$ .

- 2. Triggered by a rising edge. ADC operation can also be started by software.

- 3. RST also provides a reset pulse as output when timer T3 overflows or after a CAN wake-up from Power-down.

- 4. ALE is activated every six oscillator periods. During an external data memory access one ALE pulse is skipped.

- 5. See Section 7.1, Table 3 for EA operation. For P83Cxxx microcontrollers specified with the option 'ROM-code protection', the EA pin is latched during reset and is 'don't care' after reset, regardless of whether the ROM-code protection is selected or not.

### P8xC592

- 6. Pin 55, REF:

- a) Selection of input resp. output dependent of CAN Control Register bit 5 (CR.5; see Section 13.5.3 Table 32).

- b) If the internal reference is used, then REF should be connected to AV<sub>SS</sub> via a capacitor with a value of  $\geq$ 10 nF.

- c) After an external reset (RST = HIGH) the internal  $\frac{1}{2}$ AV<sub>DD</sub> source is activated and, REF is a reference output.

- d) If the CAN-controller is in the reset state, e.g. after an external reset, then the ½AV<sub>DD</sub> source is switched off during Power-down mode.

- 7. CAN-bus line:

- a) CRX0 level > CRX1 level is interpreted as a logic 1 (recessive).

- b) CRX0 level < CRX1 level is interpreted as a logic 0 (dominant).

- 8. The level of  $AV_{REF+}$  must be higher than that of  $AV_{REF-}$ .

#### Table 2 Pin description for pins with alternative functions (SOT188-2 and NO330; see note 1)

|              | SYMBOL      | DIN              | DESCRIPTION                                   |  |  |

|--------------|-------------|------------------|-----------------------------------------------|--|--|

| DEFAULT      | ALTERNATIVE | PIN              | DESCRIPTION                                   |  |  |

| Port 4       | -           |                  |                                               |  |  |

| P4.0 to P4.7 |             | 7 to 14          | 8-bit quasi-bidirectional I/O port.           |  |  |

|              | CMSR0       | 7                | Compare and Set/Reset outputs for Timer T2.   |  |  |

|              | CMSR1       | 8                |                                               |  |  |

|              | CMSR2       | 9                |                                               |  |  |

|              | CMSR3       | 10               |                                               |  |  |

|              | CMSR4       | 11               |                                               |  |  |

|              | CMSR5       | 12               |                                               |  |  |

| -            | CMT0        | 13               | Compare and toggle outputs for Timer T2.      |  |  |

|              | CMT1        | 14               |                                               |  |  |

| Port 1       |             |                  |                                               |  |  |

| P1.0 to P1.7 |             | 16 to 21, 23, 24 | 8-bit quasi-bidirectional I/O port.           |  |  |

|              | CT0I/INT2   | 16               | Capture timer inputs for Timer T2,            |  |  |

|              | CT1I/INT3   | 17               | or                                            |  |  |

|              | CT2I/INT4   | 18               | External interrupt inputs.                    |  |  |

|              | CT3I/INT5   | 19               |                                               |  |  |

|              | T2          | 20               | T2 event input (rising edge triggered).       |  |  |

|              | RT2         | 21               | T2 timer reset input (rising edge triggered). |  |  |

|              | CTX0        | 23               | CAN transmitter output 0 (note 2).            |  |  |

|              | CTX1        | 24               | CAN transmitter output 1 (note 2).            |  |  |

### P8xC592

| SYMBOL                 |                                   | DIN           | DECODIDITION                                                    |  |

|------------------------|-----------------------------------|---------------|-----------------------------------------------------------------|--|

| DEFAULT                | ALTERNATIVE                       | PIN           | DESCRIPTION                                                     |  |

| Port 3                 |                                   |               | ·                                                               |  |

| P3.0 to P3.7           |                                   | 25 to 32      | 8-bit quasi-bidirectional I/O port.                             |  |

|                        | RXD                               | 25            | Serial Input Port.                                              |  |

|                        | TXD                               | 26            | Serial Output Port.                                             |  |

|                        | INT0                              | 27            | External interrupt inputs.                                      |  |

|                        | INT1                              | 28            |                                                                 |  |

|                        | Т0                                | 29            | Timer 0 external input.                                         |  |

|                        | T1                                | 30            | Timer 1 external input.                                         |  |

|                        | WR                                | 31            | External Data Memory Write strobe.                              |  |

|                        | RD                                | 32            | External Data Memory Read strobe.                               |  |

| Port 2 (Sink/          | source: $1 \times TTL = 4 \times$ | LSTTL inputs) | ·                                                               |  |

| P2.0 to P2.7           |                                   | 36 to 43      | 8-bit quasi-bidirectional I/O port.                             |  |

|                        | A08 to A15                        |               | High-order address byte for external memory                     |  |

| Port 0 (Sink/          | /source: 8 × LSTTL inp            | uts)          |                                                                 |  |

| P0.7 to P0.0           |                                   | 47 to 54      | 8-bit open drain bidirectional I/O port.                        |  |

|                        | AD7 to AD0                        |               | Multiplexed Low-order address and Data bus for external memory. |  |

|                        |                                   |               | •                                                               |  |

| Port 5                 |                                   |               |                                                                 |  |

| Port 5<br>P5.7 to P5.0 |                                   | 62 to 68, 1   | 8-bit input port.                                               |  |

#### Notes

1. To avoid a 'latch up' effect at power-on:  $V_{SS} - 0.5 V <$  'voltage on any pin at any time'  $< V_{DD} + 0.5 V$ .

2. If the CAN-controller is in the reset state (e.g. after a power-up reset; CAN Control Register bit CR.0; see Section 13.5.3 Table 32), the CAN transmitter outputs are floating and the pins P1.6 and P1.7 can be used as open-drain port pins. After a power-up reset the port data is HIGH, leaving the pins P1.6 and P1.7 floating.

#### 6 FUNCTIONAL DESCRIPTION

The P8xC592 functions will be described as shown in the following overview:

- Memory organization

- I/O Port structure

- Pulse Width Modulated outputs

- Analog-to-digital Converter

- Timers/Counters

- Serial I/O Ports

- Interrupt system

- Power reduction modes

- Oscillator circuitry

- Reset circuitry

- Instruction Set.

#### 7 MEMORY ORGANIZATION

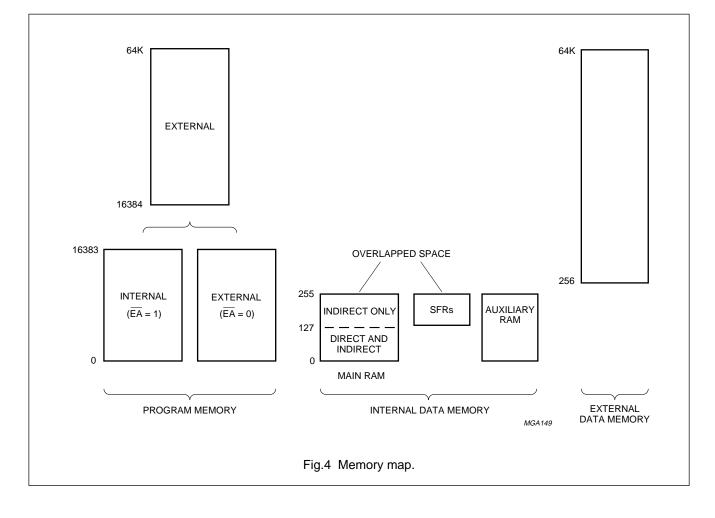

The Central Processing Unit (CPU) manipulates operands in three memory spaces (see Fig.4) as follows:

- 16 kbytes internal resp. 64 kbytes external Program Memory

- 512 bytes internal Data Memory MAIN- and AUXILIARY RAM

- up to 64 kbytes external Data Memory (with 256 bytes residing in the internal AUXILIARY RAM).

### P8xC592

#### 7.1 Program Memory

The Program Memory of the P8xC592 consists of 16 kbytes ROM on-chip, externally expandible up to 64 kbytes.

Table 3 Instruction fetch controlled by EA

| PIN EA (                    | note 1)      |                                  | ADDRESS                   |

|-----------------------------|--------------|----------------------------------|---------------------------|

| DURING RESET<br>LATCHED TO: | AFTER RESET  | INSTRUCTIONS FETCHED FROM:       | LOCATION                  |

| Н                           | _            | internal Program Memory (note 2) | $0000H \rightarrow 3FFFH$ |

| Н                           | _            | external Program Memory          | $4000H \rightarrow FFFFH$ |

| L                           | —            |                                  | $0000H \rightarrow FFFFH$ |

| _                           | 'don't care' | _                                | —                         |

#### Notes

- 1. This implementation prevents reading of the internal program code by switching from external Program Memory during a MOVC instruction.

- 2. By setting a security bit the internal Program Memory content is protected, which means it cannot be read out. If the security bit has been set to LOW there are no restrictions for the MOVC instruction.

#### 7.2 Internal Data Memory

The internal Data Memory is physically built-up and accessible as shown in Table 4 (see Fig.5).

| INTERNAL                  | SIZE LOCATION |            | ADDRES | S MODE   | POINTERS                                                                  |

|---------------------------|---------------|------------|--------|----------|---------------------------------------------------------------------------|

| DATA MEMORY               | SIZE          | LUCATION   | DIRECT | INDIRECT | FOINTERS                                                                  |

| MAIN RAM                  | 256 bytes     | 0 to 127   | Х      | Х        | address pointers are R0 and R1 of the                                     |

| (note 1)                  |               | 128 to 255 | _      | Х        | selected register bank                                                    |

| AUXILIARY RAM<br>(note 2) | 256 bytes     | 0 to 255   | _      | Х        | address pointers are R0 and R1 of the selected register bank and the DPTR |

| SFRs (note 3)             | 128 bytes     | 128 to 255 | Х      | _        | _                                                                         |

Table 4 Internal Data Memory size and address mode

#### Notes

- 1. MAIN RAM can be addressed directly and indirectly as in the 80C51.

- 2. AUXILIARY RAM (0 to 255):

- a) Is indirectly addressable in the same way as the external Data Memory with MOVX instructions.

- b) Access will not affect the ports P0, P2, P3.6 and P3.7 during internal program execution.

- 3. SFRs = Special Function Registers.

#### 7.2.1 MAIN RAM

Four 8-bit register banks occupy the lower RAM area,

- BANK 0: location 0 to 7

- BANK 1: location 8 to 15

- BANK 2: location 16 to 23

- BANK 4: location 24 to 31.

Only one of these banks may be enabled at the same time.

The next 16 bytes, locations 32 through 45, contains 128 directly addressable bit locations.

The stack can be located anywhere in the internal MAIN RAM address space. The stack depth is only limited by the internal RAM space available. All registers except the program counter and the four 8-bit register banks reside in the SFR address space.

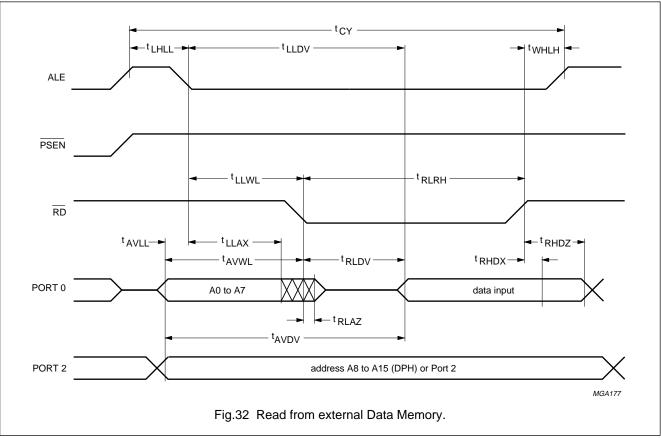

#### 7.3 External Data Memory

An access to external Data Memory locations higher than 255 will be performed with the MOVX @DPTR instructions in the same way as in the 80C51 structure,

i.e. with P0 and P2 as data/address bus and P3.6 and P3.7 as Write and Read strobe signals.

Note that these external Data Memory locations cannot be accessed with R0 or R1 as address pointer.

| 7FH  | (MS     | SB)    |    |     |      | (L | SB) | 127   |    |

|------|---------|--------|----|-----|------|----|-----|-------|----|

| :    | Ę       |        |    |     |      |    |     | 2     | Ļ  |

|      |         |        |    |     |      |    |     |       |    |

|      |         |        |    |     |      |    |     |       |    |

| 2FH  | 7F      | 7E     | 7D | 7C  | 7B   | 7A | 79  | 78    | 47 |

| 2EH  | 77      | 76     | 75 | 74  | 73   | 72 | 71  | 70    | 46 |

| 2DH  | 6F      | 6E     | 6D | 6C  | 6B   | 6A | 69  | 68    | 45 |

| 2CH  | 67      | 66     | 65 | 64  | 63   | 62 | 61  | 60    | 44 |

| 2BH  | 5F      | 5E     | 5D | 5C  | 5B   | 5A | 59  | 58    | 43 |

| 2AH  | 57      | 56     | 55 | 54  | 53   | 52 | 51  | 50    | 42 |

| 29H  | 4F      | 4E     | 4D | 4C  | 4B   | 4A | 49  | 48    | 41 |

| 28H  | 47      | 46     | 45 | 44  | 43   | 42 | 41  | 40    | 40 |

| 27H  | 3F      | 3E     | 3D | 3C  | 3B   | ЗA | 39  | 38    | 39 |

| 26H  | 37      | 36     | 35 | 34  | 33   | 32 | 31  | 30    | 38 |

| 25H  | 2F      | 2E     | 2D | 2C  | 2B   | 2A | 29  | 28    | 37 |

| 24H  | 27      | 26     | 25 | 24  | 23   | 22 | 21  | 20    | 36 |

| 23H  | 1F      | 1E     | 1D | 1C  | 1B   | 1A | 19  | 18    | 35 |

| 22H  | 17      | 16     | 15 | 14  | 13   | 12 | 11  | 10    | 34 |

| 21H  | 0F      | 0E     | 0D | 0C  | 0B   | 0A | 09  | 08    | 33 |

| 20H  | 07      | 06     | 05 | 04  | 03   | 02 | 01  | 00    | 32 |

| 1FH  |         |        |    |     |      |    |     |       | 31 |

|      |         | BANK 3 |    |     |      |    |     |       |    |

| 18H  |         |        |    |     |      |    |     |       | 24 |

| 17H  |         |        |    |     |      |    |     |       | 23 |

|      |         |        |    | BAN | VK 2 |    |     |       |    |

| 10H  |         |        |    |     |      |    |     |       | 16 |

| 0FH  |         |        |    |     |      |    |     |       | 15 |

|      | BANK 1  |        |    |     |      |    |     |       |    |

| 08H  |         |        |    |     |      |    |     | 8     |    |

| 07H  |         |        |    |     |      |    |     | 7     |    |

|      | BANK 0  |        |    |     |      |    |     |       |    |

| 00H  | DAINE U |        |    |     |      |    |     | 0     |    |

| 0011 |         |        |    |     |      |    |     |       | j  |

|      |         |        |    |     |      |    | M   | GA152 |    |

|      |         |        |    |     |      |    |     | ress  |    |

## P8xC592

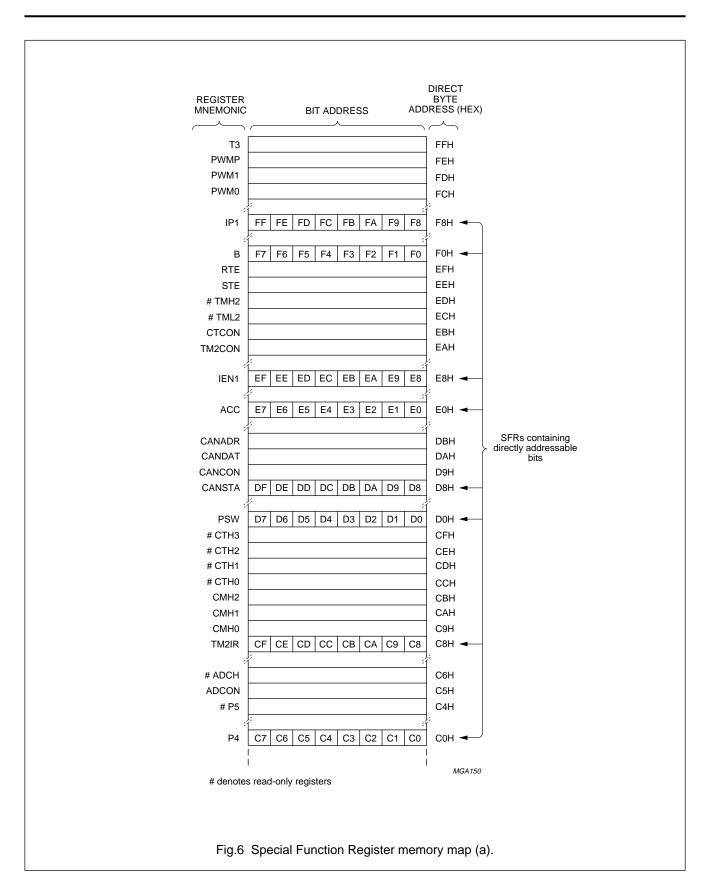

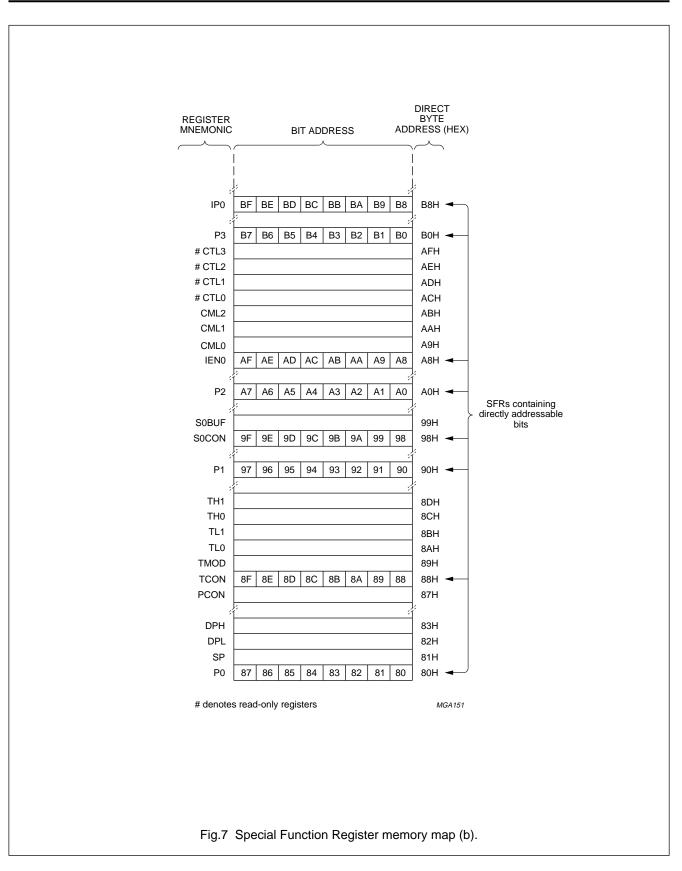

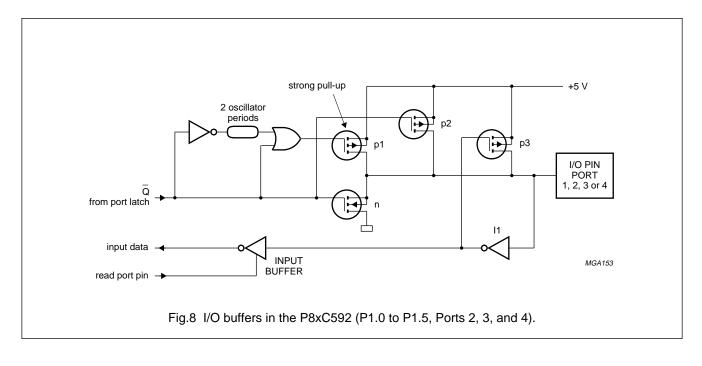

### 8 I/O PORT STRUCTURE

The P8xC592 has six 8-bit parallel ports: Port 0 to Port 5. In addition to the standard 8-bit parallel ports, the I/O facilities also include a number of special I/O lines. The use of a Port 1, Port 3 or Port 4 pins as an alternative function is carried out automatically provided the associated SFR bit is set HIGH.

| PORT   | TYPE | FUNCTION                                        | REMARKS                                                          |

|--------|------|-------------------------------------------------|------------------------------------------------------------------|

| Port 0 | I/O  | The same as in the 80C51                        | Except for the additional functions of P1.6 and                  |

| Port 1 | I/O  |                                                 | P1.7.                                                            |

| Port 2 | I/O  |                                                 |                                                                  |

| Port 3 | I/O  |                                                 |                                                                  |

| Port 4 | I/O  | Parallel I/O port                               | Parallel I/O function is identical to Port1, 2 and 3.            |

| Port 5 | I    | Parallel input port with an input function only | May be used as normal inputs if the ADC function is inoperative. |

#### Table 5 Default Port functions

#### Table 6 Alternative Port functions

| PORT       | TYPE | FUNCTION                                                                                                       | REMARKS                                                                                                                                 |  |  |  |

|------------|------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port 0     | I/O  | Multiplexed Low-order address and<br>Data bus for external memory (AD7 to AD0)                                 | Provides the multiplexed Low-order address and data bus used for expanding the P8xC592 with standard memories and peripherals.          |  |  |  |

| Port 1     | I/O  | Capture timer inputs for Timer T2<br>(CT0I to CT3I), or<br>External interrupt request inputs<br>(INT2 to INT5) | External interrupt request inputs, if capture information is not utilized.                                                              |  |  |  |

|            |      | T2 event input (T2)                                                                                            | External counter input.                                                                                                                 |  |  |  |

|            |      | T2 timer reset input (RT2)                                                                                     | External counter reset input.                                                                                                           |  |  |  |

|            |      | CAN transmitter output 0 (CTX0)                                                                                | CTX0 and CTX1 outputs of the CAN interface                                                                                              |  |  |  |

|            |      | CAN transmitter output 1 (CTX1)                                                                                | (note 1).                                                                                                                               |  |  |  |

| Port 2     | I/O  | High-order address byte for external memory (A08 to A15)                                                       | Port 2 provides the High-order address bus when<br>the P8xC592 is expanded with external Program<br>Memory and/or external Data Memory. |  |  |  |

| Port 3     | I/O  | Serial Input Port (RXD)                                                                                        | Receiver input of serial port SIO0 (UART).                                                                                              |  |  |  |

|            |      | Serial Output Port (TXD)                                                                                       | Transmitter output of serial port SIO0 (UART).                                                                                          |  |  |  |

|            |      | External interrupt (INT0)                                                                                      | External interrupt request inputs.                                                                                                      |  |  |  |

|            |      | External interrupt (INT1)                                                                                      |                                                                                                                                         |  |  |  |

|            |      | Timer 0 external input (T0)                                                                                    | Counter inputs.                                                                                                                         |  |  |  |

|            |      | Timer 1 external input (T1)                                                                                    |                                                                                                                                         |  |  |  |

|            |      | External data memory Write strobe ( $\overline{WR}$ )                                                          | Control signal to write to external Data Memory.                                                                                        |  |  |  |

|            |      | External data memory Read strobe $(\overline{RD})$                                                             | Control signal to read from external Data Memory.                                                                                       |  |  |  |

| Port 4 I/O |      | Compare and Set/Reset outputs<br>(CMSR0 to CMSR5)                                                              | Can be configured to provide signals indicating a match between Timer counter T2 and its compare                                        |  |  |  |

|            |      | Compare and toggle outputs (CMT0, CMT1)                                                                        | registers.                                                                                                                              |  |  |  |

| Port 5     | I    | Input channels to ADC (ADC7 to ADC0)                                                                           | Port 5 may be used in conjunction with the ADC interface (note 2).                                                                      |  |  |  |

#### Notes to the alternative Port functions

- 1. Port lines P1.6 and P1.7 may be selected as CTX0 and CTX1 outputs of the serial port SIO1 (CAN). After reset P1.6 and P1.7 may be used as normal I/O ports, if the CAN interface is not used.

- Unused analog inputs can be used as digital inputs. As Port 5 lines may be used as inputs to the ADC, these digital inputs have an inherent hysteresis to prevent the input logic from drawing too much current from the power lines when driven by analog signals.

Channel-to-channel crosstalk should be taken into consideration when both digital and analog signals are simultaneously input to Port 5 (see Chapter 20).

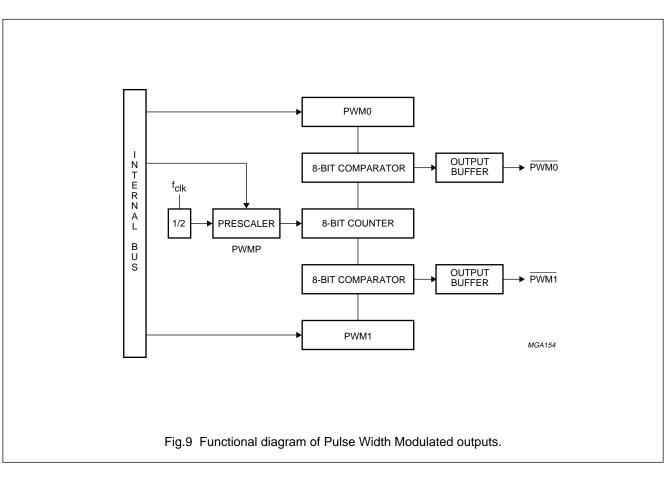

#### 9 PULSE WIDTH MODULATED OUTPUTS (PWM)

Two Pulse Width Modulated (PWM) output channels are available with the P8xC592. These channels provide output pulses of programmable length and interval. The repetition frequency is defined by an 8-bit prescaler PWMP which generates the clock for the counter. Both the prescaler and counter are common to both PWM channels. The 8-bit counter counts modulo 255 i.e. from 0 to 254 inclusive. The value of the 8-bit counter is compared to the contents of two registers: PWM0 and PWM1.

Provided the contents of either of these registers is greater than the counter value, the output of  $\overline{PWM0}$  or  $\overline{PWM1}$  is set LOW. If the contents of these register are equal to, or less than the counter value, the output will be HIGH. The pulse-width-ratio is therefore defined by the contents of the register PWM0 and PWM1. The pulse-width-ratio is in the range of 0 to  $^{255}/_{255}$  and may be programmed in increments of  $^{1}/_{255}$ .

The repetition frequency  $f_{PWM}$ , at the  $\overline{PWMn}$  outputs is

given by:

$$f_{PWM} = \frac{f_{CLK}}{2 \times (PWMP + 1) \times 255}$$

When using an oscillator frequency of 16 MHz, for example, the above formula would give a repetition frequency range of 123 Hz to 31.4 kHz.

By loading the PWM registers with either 00H or FFH, the PWM outputs can be retained at a constant HIGH or LOW level respectively. When loading FFH to the PWM registers, the 8-bit counter will never actually reach this (FFH) value.

Both output pins  $\overline{PWMn}$  are driven by push-pull drivers, and are not shared with any other function.

#### 9.1 Prescaler frequency control register (PWMP)

Table 7 Prescaler frequency control register (address FEH)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PWMP.7 | PWMP.6 | PWMP.5 | PWMP.4 | PWMP.3 | PWMP.2 | PWMP.1 | PWMP.0 |

#### Table 8 Description of PWMP bits

| BIT | SYMBOL | FUNCTION                                    |

|-----|--------|---------------------------------------------|

| 7   | PWMP.7 | Prescaler division factor.                  |

| to  | to     | The Prescaler division factor = (PWMP) + 1. |

| 0   | PWMP.0 |                                             |

#### 9.2 Pulse Width Register 0 (PWM0)

#### Table 9 Pulse Width Register (address FCH)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PWM0.7 | PWM0.6 | PWM0.5 | PWM0.4 | PWM0.3 | PWM0.2 | PWM0.1 | PWM0.0 |

#### Table 10 Description of PWM0 bits

| BIT | SYMBOL | FUNCTION                                                              |  |  |  |  |

|-----|--------|-----------------------------------------------------------------------|--|--|--|--|

| 7   | PWM0.7 | Pulse width ratio.                                                    |  |  |  |  |

| to  | to     | LOW/HIGH ratio of $\overline{PWMn}$ signals = $\frac{(PWMn)}{(PWMn)}$ |  |  |  |  |

| 0   | PWM0.0 | 255 - (PWMn)                                                          |  |  |  |  |

#### 9.3 Pulse Width Register 1 (PWM1)

#### Table 11 Pulse width register (address FDH)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |   |

|--------|--------|--------|--------|--------|--------|--------|--------|---|

| PWM1.7 | PWM1.6 | PWM1.5 | PWM1.4 | PWM1.3 | PWM1.2 | PWM1.1 | PWM1.0 | ] |

#### Table 12 Description of PWM1 bits

| BIT | SYMBOL | FUNCTION                                                           |  |  |  |

|-----|--------|--------------------------------------------------------------------|--|--|--|

| 7   | PWM1.7 | Pulse width ratio.                                                 |  |  |  |

| to  | to     | LOW/HIGH ratio of $\overline{PWMn}$ signals = $\frac{(PWMn)}{255}$ |  |  |  |

| 0   | PWM1.0 | 255 - (PWMn)                                                       |  |  |  |

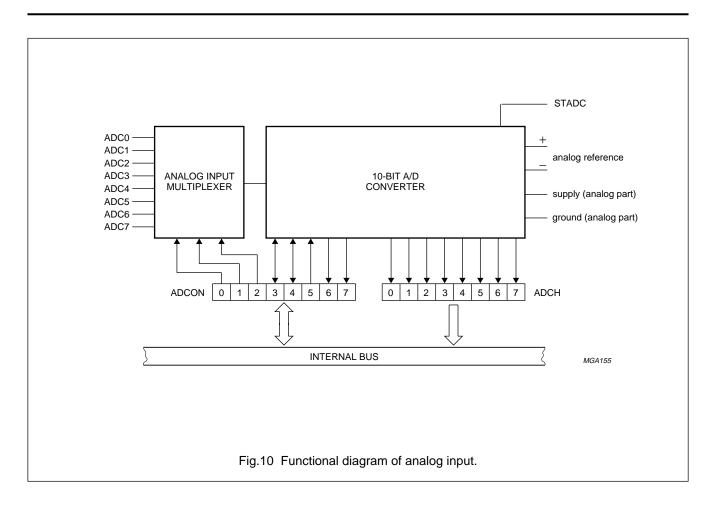

#### 10 ANALOG-TO-DIGITAL CONVERTER (ADC)

The analog input circuitry consists of an 8-input analog multiplexer and an ADC with 10-bit resolution. The analog reference voltage and analog power supplies are connected via separate input pins. The conversion takes 50 machine cycles i.e.  $37.5 \ \mu$ s at 16 MHz oscillator frequency. The input voltage swing is from 0 V to AV<sub>DD</sub>. The ADC is controlled using the ADCON control register. Register bits ADCON.0 to ADCON.2 select the input channels of the analog multiplexer (see Fig.10). The completion of the 10-bit analog-to-digital conversion is flagged by ADCI in the ADCON register and the result is stored in the SFR ADCH (upper 8-bits) and the 2 lower bits (ADC.1 and ADC.0) in register ADCON.

An analog-to-digital conversion in progress is unaffected by an external or software ADC start. The result of a completed conversion remains unchanged provided ADCI = HIGH. While ADCI or ADCS are HIGH, a new ADC START will be blocked and consequently lost. An analog-to-digital conversion already in progress is aborted when the Idle or Power-down mode is entered. The result of a completed conversion (ADCI = HIGH) remains unaffected during the Idle mode. The LOW-to-HIGH transition of STADC is recognized at the end of a machine cycle and the conversion commences at the beginning of the next cycle. When a conversion is initiated by software, the conversion starts at the beginning of the machine cycle following the instruction that sets ADCS.

The next two machine cycles are used to initiate the converter. At the end of this first cycle, the ADCS status flag is set to HIGH while the conversion is in progress. Sampling of the analog input commences at the end of the second cycle.

During the next eight machine cycles, the voltage at the previously selected pin of Port 5 is sampled and this input voltage should be stable in order to obtain a useful sample. In any case, the input voltage slew rate must be less than 10 V/ms (5 V conversion range) in order to prevent an undefined result. The conversion takes four machine cycles per bit.

### P8xC592

#### 10.1 ADC Control register (ADCON)

Table 13 ADC Control register (address C5H)

| 7     | 6     | 5    | 4    | 3    | 2     | 1     | 0     |

|-------|-------|------|------|------|-------|-------|-------|

| ADC.1 | ADC.0 | ADEX | ADCI | ADCS | AADR2 | AADR1 | AADR0 |

#### Table 14 Description of the ADCON bits

| BIT | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7   | ADC.1  | Bit 1 of ADC converted value.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 6   | ADC.0  | Bit 0 of ADC converted value.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 5   | ADEX   | nable external start of conversion by STADC. If ADEX is:                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|     |        | LOW, then conversion cannot be started externally by STADC (only by software by setting ADCS)                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|     |        | HIGH, then conversion can be started externally by a rising edge on STADC or externally.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 4   | ADCI   | <b>DC interrupt flag.</b> This flag is set when an analog-to-digital conversion result is ready to be read.<br>enabled, an interrupt is invoked. The flag must be cleared by software.<br>cannot be set by software (see Table 15).                                                                                                                                      |  |  |  |  |  |  |

| 3   | ADCS   | <b>ADC start and status.</b> Setting this bit starts an analog-to-digital conversion. It may be set by software or by the external signal STADC. The ADC logic ensures that this signal is HIGH while the ADC is busy. On completion of the conversion, ADCS is reset at the same time the interrupt flag ADCI is set. ADCS can not be reset by software (see Table 15). |  |  |  |  |  |  |

| 2   | AADR2  | Analog input select. This binary coded address selects one of the eight analog port pins of P5 to be                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 1   | AADR1  | input to the converter. It can only be changed when ADCI and ADCS are both LOW. AADR2 is the                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 0   | AADR0  | MSB. (e.g. 100B selects the analog input channel ADC4)                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

#### Table 15 ADCI and ADCS operating modes

If ADCI is cleared by software while ADCS is set at the same time a new analog-to-digital conversion with the same channel-number may be started. It is recommended to reset ADCI before ADCS is set.

| ADCI | ADCS           | OPERATION                                       |  |  |

|------|----------------|-------------------------------------------------|--|--|

| 0    | 0              | ADC not busy, a conversion can be started.      |  |  |

| 0    | 1              | ADC busy, start of a new conversion is blocked. |  |  |

| 1    | X (don't care) | Conversion completed; see note 1.               |  |  |

#### Note

1. Start of a new conversion requires ADCI = 0.

### P8xC592

#### 11 TIMERS/COUNTERS

The P8xC592 contains:

- Three 16-bit timer/event counters: Timer 0, Timer 1 and Timer T2

- One 8-bit timer, T3 (Watchdog WDT).

#### 11.1 Timer 0 and Timer 1

Timer 0 and Timer 1 may be programmed to carry out the following functions:

- · Measure time intervals and pulse durations

- Count events

- Generate interrupt requests.

Timer 0 and Timer 1 can be programmed independently to operate in 3 modes:

- Mode 0 8-bit timer or 8-bit counter each with divide-by-32 prescaler.

- Mode 1 16-bit timer-interval or event counter.

- Mode 2 8-bit timer-interval or event counter with automatic reload upon overflow.

Timer 0 can be programmed to operate in an additional mode as follows:

Mode 3 one 8-bit time-interval or event counter and one 8-bit timer-interval counter.

When Timer 0 is in Mode 3, Timer 1 can be programmed to operate in Modes 0, 1 or 2 but cannot set an interrupt flag or generate an interrupt. However, the overflow from Timer 1 can be used to pulse the Serial Port baud-rate generator.

The frequency handling range of these counters with a 16 MHz crystal is as follows:

- In the timer function, the timer is incremented at a frequency of 1.33 MHz (<sup>1</sup>/<sub>12</sub> of the oscillator frequency)

- 0 Hz to an upper limit of 0.66 MHz (<sup>1</sup>/<sub>24</sub> of the oscillator frequency) when programmed for external inputs.

Both internal and external inputs can be gated to the counter by a second external source for directly measuring pulse durations. When configured as a counter, the register is incremented on every falling edge on the corresponding input pin, T0 or T1.

The earliest moment, when the incremented register value can be read is during the second machine cycle following the machine cycle within which the incrementing pulse occurred. The counters are started and stopped under software control. Each one sets its interrupt request flag when it overflows from all HIGHs to all LOWs (or automatic reload value), with the exception of Mode 3 as previously described.

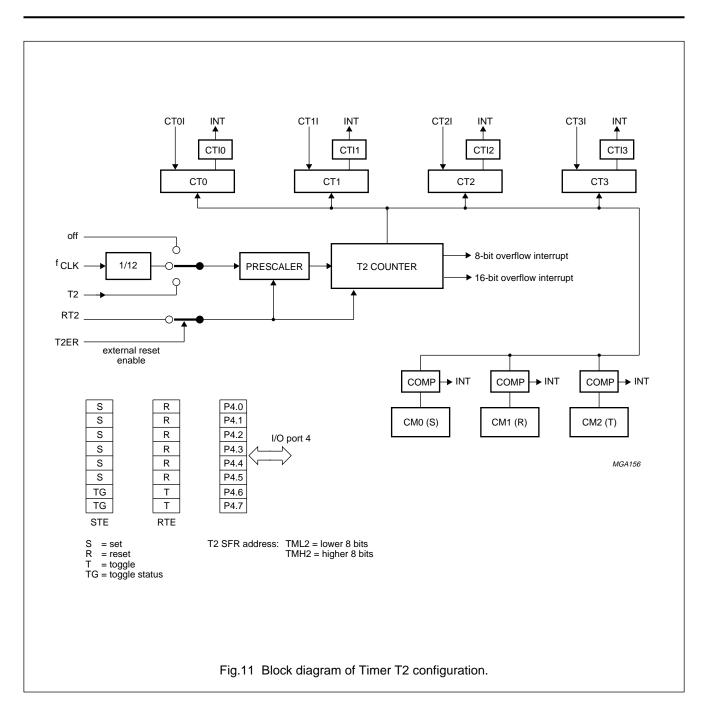

#### 11.2 Timer T2 Capture and Compare Logic

Timer T2 is a 16-bit timer/counter which has capture and compare facilities (see Fig.11).

The 16-bit timer/counter is clocked via a prescaler with a programmable division factor of 1, 2, 4 or 8. The input of the prescaler is clocked with  $\frac{1}{12}$  of the oscillator frequency, or by an external source connected to the T2 input, or it is switched off. The maximum repetition rate of the external clock source is  $\frac{1}{12}f_{CLK}$ , twice that of Timer 0 and Timer 1. The prescaler is incremented on a rising edge. It is cleared if its division factor or its input source is changed, or if the timer/counter is reset.

T2 is readable 'on the fly', without any extra read latches; this means that software precautions have to be taken against misinterpretation at overflow from least to most significant byte while T2 is being read. T2 is not loadable and is reset by the RST signal or at the positive edge of the input signal RT2, if enabled. In the Idle mode the timer/counter and prescaler are reset and halted.

T2 is connected to four 16-bit Capture Registers: CT0, CT1, CT2 and CT3. A rising or falling edge on the inputs CT0I, CT1I, CT2I or CT3I (alternative function of Port 1) results in loading the contents of T2 into the respective Capture Registers and an interrupt request.

Using the Capture Register CTCON, these inputs may invoke capture and interrupt request on a positive edge, a negative edge or on both edges. If neither a positive nor a negative edge is selected for capture input, no capture or interrupt request can be generated by this input.

The contents of the Compare Registers CM0, CM1 and CM2 are continually compared with the counter value of Timer T2. When a match occurs, an interrupt may be invoked. A match of CM0 sets the bits 0 to 5 of Port 4, a CM1 match resets these bits and a CM2 match toggles bits 6 and 7 of Port 4, provided these functions are enabled by the STE/RTE registers. A match of CM0 and CM1 at the same time results in resetting bits 0 to 5 of Port 4. CM0, CM1 and CM2 are reset by the RST signal.

Port 4 can be read and written by software without affecting the toggle, set and reset signals. At a byte overflow of the least significant byte, or at a 16-bit overflow of the timer/counter, an interrupt sharing the same interrupt vector is requested. Either one or both of these overflows can be programmed to request an interrupt. All interrupt flags must be reset by software.

## P8xC592

11.2.1 COUNTER CONTROL REGISTER (TM2CON)

Table 16 Counter Control register (address EAH)

| 7     | 6     | 5    | 4    | 3    | 2    | 1     | 0     |

|-------|-------|------|------|------|------|-------|-------|

| T2IS1 | T2IS0 | T2ER | T2B0 | T2P1 | T2P0 | T2MS1 | T2MS0 |

#### Table 17 Description of the TM2CON bits

| BIT | SYMBOL | FUNCTION                                  |  |  |  |

|-----|--------|-------------------------------------------|--|--|--|

| 7   | T2IS1  | Timer 2 16-bit overflow interrupt select. |  |  |  |

| 6   | T2IS0  | Timer 2 byte overflow interrupt select.   |  |  |  |

| 5   | T2ER   | Timer 2 external reset enable.            |  |  |  |

| 4   | T2B0   | Timer 2 byte overflow interrupt flag.     |  |  |  |

| 3   | T2P1   | Timer 2 prescaler select (see Table 18).  |  |  |  |

| 2   | T2P0   |                                           |  |  |  |

| 1   | T2MS1  | Timer 2 mode select (see Table 19).       |  |  |  |

| 0   | T2MS0  |                                           |  |  |  |

#### Table 18 Timer 2 prescaler select

| T2P1 | T2P0 | T2 CLOCK                                 |  |  |

|------|------|------------------------------------------|--|--|

| 0    | 0    | Clock source                             |  |  |

| 0    | 1    | <sup>1</sup> / <sub>2</sub> Clock source |  |  |

| 1    | 0    | 1/4 Clock source                         |  |  |

| 1    | 1    | <sup>1</sup> / <sub>8</sub> Clock source |  |  |

#### Table 19 Timer 2 mode select

| T2MS1 | T2MS0 MODE           |                                            |

|-------|----------------------|--------------------------------------------|

| 0     | 0 Timer T2 is halted |                                            |

| 0     | 1                    | T2 clock source = $\frac{1}{12} f_{CLK}$ . |

| 1     | 0                    | Test mode; do not use                      |

| 1     | 1                    | T2 clock source = pin T2                   |

#### 11.2.2 CAPTURE CONTROL REGISTER (CTCON)

#### Table 20 Capture Control register (address EBH)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| CTN3 | CTP3 | CTN2 | CTP2 | CTN1 | CTP1 | CTN0 | CTP0 |

Table 21 Description of the CTCON bits

| DIT | SYMBOL |         | FUNCTION      |  |  |  |  |  |

|-----|--------|---------|---------------|--|--|--|--|--|

| BIT |        | CAPTURE | INTERRUPT ON  |  |  |  |  |  |

| 7   | CTN3   | СТЗІ    | negative edge |  |  |  |  |  |

| 6   | CTP3   | СТЗІ    | positive edge |  |  |  |  |  |

| 5   | CTN2   | CT2I    | negative edge |  |  |  |  |  |

| 4   | CTP2   | CT2I    | positive edge |  |  |  |  |  |

| 3   | CTN1   | CT1I    | negative edge |  |  |  |  |  |

| 2   | CTP1   | CT1I    | positive edge |  |  |  |  |  |

| 1   | CTN0   | СТОІ    | negative edge |  |  |  |  |  |

| 0   | CTP0   | CT0I    | positive edge |  |  |  |  |  |

### P8xC592

11.2.3 TIMER INTERRUPT FLAG REGISTER (TM2IR)

#### Table 22 Timer Interrupt Flag register (address C8H)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| T2OV | CMI2 | CMI1 | CMI0 | CTI3 | CTI2 | CTI1 | CTI0 |

#### Table 23 Description of the TM2IR bits (see notes 1 and 2)

| BIT | SYMBOL | FUNCTION                           |

|-----|--------|------------------------------------|

| 7   | T2OV   | T2: 16-bit overflow interrupt flag |

| 6   | CMI2   | CM2: interrupt flag                |

| 5   | CMI1   | CM1: interrupt flag                |

| 4   | CMI0   | CM0: interrupt flag                |

| 3   | CTI3   | CT3: interrupt flag                |

| 2   | CTI2   | CT2: interrupt flag                |

| 1   | CTI1   | CT1: interrupt flag                |

| 0   | CTI0   | CT0: interrupt flag                |

#### Notes

- 1. Interrupt Enable IEN1 is used to enable/disable Timer 2 interrupts (see Section 14.1.2).

- 2. Interrupt Priority Register IP1 is used to determine the Timer 2 interrupt priority (see Section 14.1.4).

#### 11.2.4 SET ENABLE REGISTER (STE)

Table 24

Set Enable register (address EEH)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| TG47 | TG46 | SP45 | SP44 | SP43 | SP42 | SP41 | SP40 |

#### **Table 25** Description of the STE bits (see notes 1 and 2)

| BIT | SYMBOL | FUNCTION                                                                             |

|-----|--------|--------------------------------------------------------------------------------------|

| 7   | TG47   | if HIGH then P4.7 is reset on the next toggle, if LOW P4.7 is set on the next toggle |

| 6   | TG46   | if HIGH then P4.6 is reset on the next toggle, if LOW P4.6 is set on the next toggle |

| 5   | SP45   | if HIGH then P4.5 is set on a match of CM0 and T2                                    |

| 4   | SP44   | if HIGH then P4.4 is set on a match of CM0 and T2                                    |

| 3   | SP43   | if HIGH then P4.3 is set on a match of CM0 and T2                                    |

| 2   | SP42   | if HIGH then P4.2 is set on a match of CM0 and T2                                    |

| 1   | SP41   | if HIGH then P4.1 is set on a match of CM0 and T2                                    |

| 0   | SP40   | if HIGH then P4.0 is set on a match of CM0 and T2                                    |

#### Notes

- 1. If STE.n is LOW then P4.n is not affected by a match of CM0 and T2 (n = 0, 1, 2, 3, 4, 5).

- 2. STE.6 and STE.7 are read only.

### P8xC592

11.2.5 RESET/TOGGLE ENABLE REGISTER (RTE)

Table 26 Reset/Toggle Enable register (address EFH)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| TP47 | TP46 | RP45 | RP44 | RP43 | RP42 | RP41 | RP40 |

#### Table 27 Description of the RTE bits (note 1)

| BIT | SYMBOL | FUNCTION                                            |

|-----|--------|-----------------------------------------------------|

| 7   | TP47   | if HIGH then P4.7 toggles on a match of CM2 and T2  |

| 6   | TP46   | if HIGH then P4.6 toggles on a match of CM2 and T2  |

| 5   | RP45   | if HIGH then P4.5 is reset on a match of CM1 and T2 |

| 4   | RP44   | if HIGH then P4.4 is reset on a match of CM1 and T2 |

| 3   | RP43   | if HIGH then P4.3 is reset on a match of CM1 and T2 |

| 2   | RP42   | if HIGH then P4.2 is reset on a match of CM1 and T2 |

| 1   | RP41   | if HIGH then P4.1 is reset on a match of CM1 and T2 |

| 0   | RP40   | if HIGH then P4.0 is reset on a match of CM1 and T2 |

#### Note

1. If RTE.n is LOW then P4.n is not affected by a match of CM1 and T2 or CM2 and T2. For more information, refer to the 8051-based *"8-bit Microcontrollers Data Handbook IC20"*.

## P8xC592

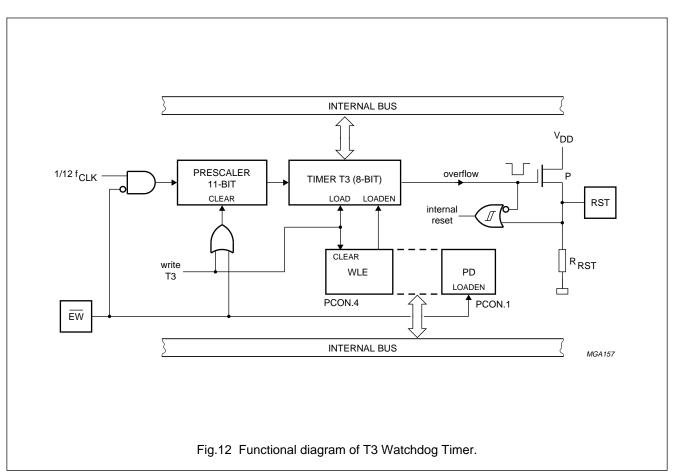

#### 11.3 Watchdog Timer (T3)

In addition to Timer T2 and the standard timers (Timer 0 and Timer 1), a Watchdog Timer (WDT) comprising an 11-bit prescaler and an 8-bit timer (T3) is also provided (see Fig.12).

The timer T3 is incremented every 1.5 ms, derived from the oscillator frequency of 16 MHz by the following

formula:  $f_{timer} = \frac{f_{CLK}}{12 \times 2048}$

When a timer T3 overflow occurs, the microcontroller is reset and a reset-output-pulse is generated at pin RST. This short output pulse (3 machine cycles) may be suppressed if the RST pin is connected to a capacitor.

To prevent a system reset (by an overflow of the WDT), the user program has to reload T3 within periods that are shorter than the programmed Watchdog time interval.

If the processor suffers a hardware/software malfunction, the software will fail to reload the timer. This failure will produce a reset upon overflow thus preventing the processor running out of control. The Watchdog Timer can only be reloaded if the condition flag WLE = PCON.4 has been previously set by software. At the moment the counter is loaded the condition flag is automatically cleared.

The timer interval between the timer's reloading and the occurrence of a reset depends on the reloaded value. For example, this may range from 1.5 ms to 0.375 s when using an oscillator frequency of 16 MHz.

In the Idle state the Watchdog Timer and reset circuitry remain active.

The Watchdog Timer (WDT) is controlled by the Enable Watchdog pin  $(\overline{EW})$  (see Table 28).

Table 28 EW controlling WDT and Power-down mode

| PIN EW | WDT      | POWER-DOWN MODE |

|--------|----------|-----------------|

| LOW    | enabled  | disabled        |

| HIGH   | disabled | enabled         |

#### 12 SERIAL I/O PORT: SIO0 (UART)

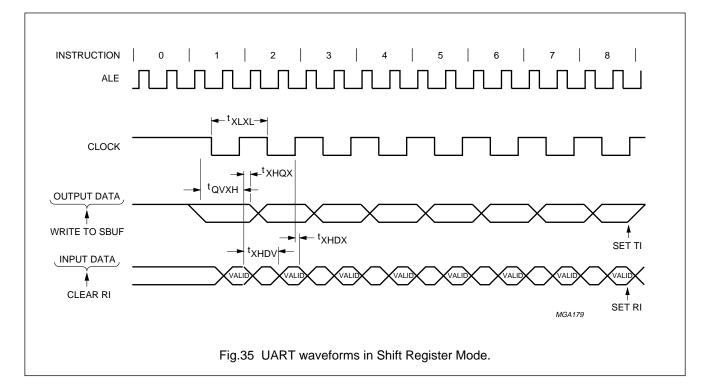

The Serial Port SIO0 is a full duplex (UART) serial I/O port i.e. it can transmit and receive simultaneously. This Serial Port is also receive-buffered. It can commence reception of a second byte before the previously received byte has been read from the receive register. However, if the first byte has still not been read by the time reception of the second byte is complete, one of these (first or second) bytes will be lost. The SIO0 receive and transmit registers are both accessed via the SOBUF SFR. Writing to SOBUF loads the transmit register, and reading SOBUF accesses to a physically separate receive register. SIO0 can operate in 4 modes:

- Mode 0 Serial data is transmitted and received through RXD. TXD outputs the shift clock. 8 data bits are transmitted/received (LSB first). The baud rate is fixed at  $\frac{1}{12}$  of the oscillator frequency.

- Mode 1 10 bits are transmitted via TXD or received through RXD: a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit is put into RB8 of the S0CON SFR. The baud rate is variable.

- Mode 2 11 bits are transmitted through TXD or received through RXD: a start bit (0), 8 data bits (LSB first), a programmable 9<sup>th</sup> data bit, and a stop bit (1). On transmit, the 9<sup>th</sup> data bit (TB8 in S0CON) can be assigned the value of 0 or 1. With nominal software, TB8 can be the parity bit (P in PSW). During a receive, the 9<sup>th</sup> data bit is stored in RB8 (S0CON), and the stop bit is ignored. The baud rate is programmable to either  $1_{32}$  or  $1_{64}$  of the oscillator frequency.

- Mode 3 11 bits are transmitted through TXD or received through RXD: a start bit (0), 8 data bits (LSB first), a programmable 9<sup>th</sup> data bit, and a stop bit (1). Mode 3 is the same as Mode 2 except for the baud rate which is variable in Mode 3.

In all four modes, transmission is initiated by any instruction that writes to the S0BUF SFR. Reception is initiated in Mode 0 when RI = 0 and REN = 1. In the other three modes, reception is initiated by the incoming start bit provided that REN = 1.

Modes 2 and 3 are provided for multiprocessor communications. In these modes, 9 data bits are received with the 9<sup>th</sup> bit written to RB8 (S0CON). The 9<sup>th</sup> bit is followed by the stop bit. The port can be programmed so that with receiving the stop bit, the Serial Port interrupt will be activated if, and only if RB8 = 1. This feature is enabled by setting bit SM2 in S0CON. This feature may be used in multiprocessor systems.

For more information about how to use the UART in combination with the registers S0CON, PCON, IE, SBUF and the Timer register, refer to the 8051-based *"8-bit Microcontrollers Data Handbook IC20"*.

#### 13 SERIAL I/O PORT: SIO1 (CAN)

SIO1 (CAN) provides the CAN (Controller Area Network) serial-bus data communication interface. SIO1 (CAN) replaces the SIO1 (I<sup>2</sup>C) serial interface as provided in the microcontroller derivative P8xC552.

#### 13.1 On-chip CAN-controller

CAN is the definition of a high performance communication protocol for serial data communication. The P8xC592 on-chip CAN-controller is a full implementation of the CAN 2.0A protocol. With the P8xC592 powerful local networks can be built, both for automotive and general industrial environments. This results in a much reduced wiring harness and enhanced diagnostic and supervisory capabilities.

#### 13.2 CAN Features

- Multi-master architecture

- Bus access priority determined by the message identifier

- 2032 message identifier (2<sup>11</sup> standard frame CAN 2.0A)

- · Guaranteed latency time for high priority messages

- Powerful error handling capability

- Data length from 0 up to 8 bytes

- Multicast and broadcast message facility

- Non destructive bit-wise arbitration

- Non-return-to-zero (NRZ) coding/decoding with bit-stuffing

- Programmable transfer rate (up to 1 Mbit/s)

- Programmable output driver configuration

- Suitable for use in a wide range of networks including the SAE's network classes A, B and C

- DMA providing high-speed on-chip data exchange

- Bus failure management facility

- <sup>1</sup>/<sub>2</sub>AV<sub>DD</sub> reference voltage.

## P8xC592

#### 13.3 Interface between CPU and CAN

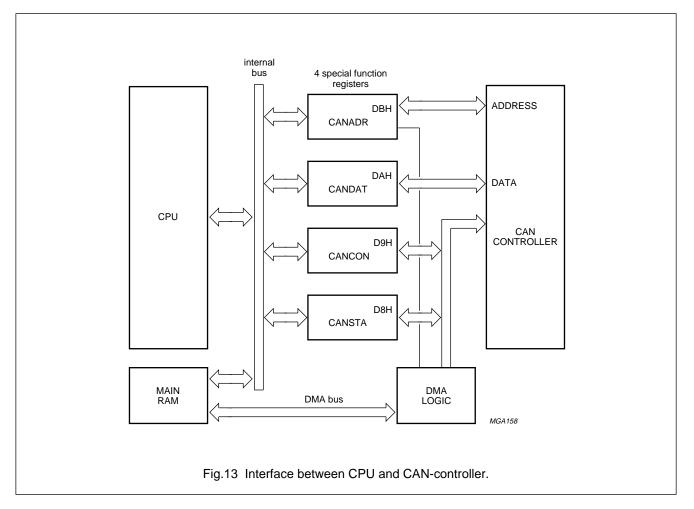

The internal interface between the P8xC592's CPU and on-chip CAN-controller is achieved via the following four SFRs (see Fig.13):

- CANADR, to point to a register of the CAN-controller

- CANDAT, to read or write data

- · CANCON, to read interrupt flags and to write commands

- CANSTA, to read status information and to write DMA pointer.

Additionally, the DMA-logic allows a high-speed data exchange between the CAN-controller and the CPU's on-chip MAIN RAM. For more information, see Section 13.5.15 "Handling of the CPU-CAN interface".

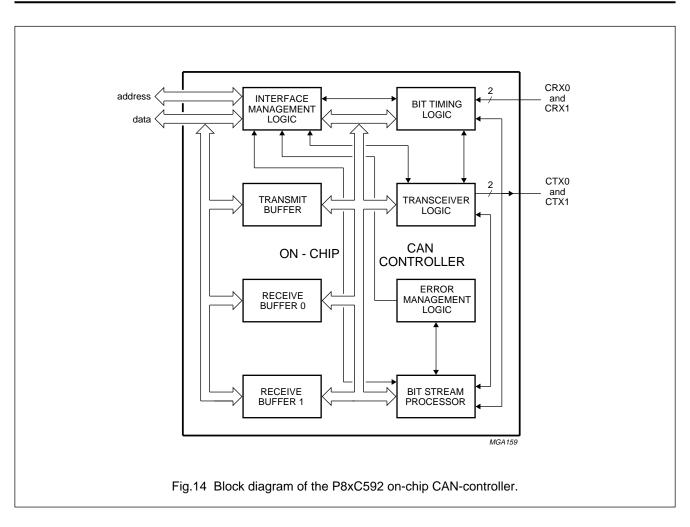

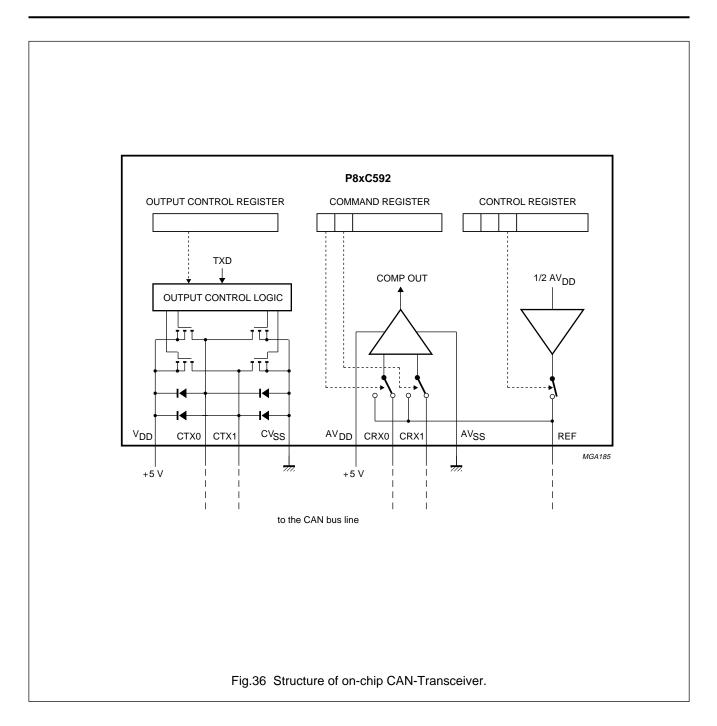

#### 13.4 Hardware blocks of the CAN-controller

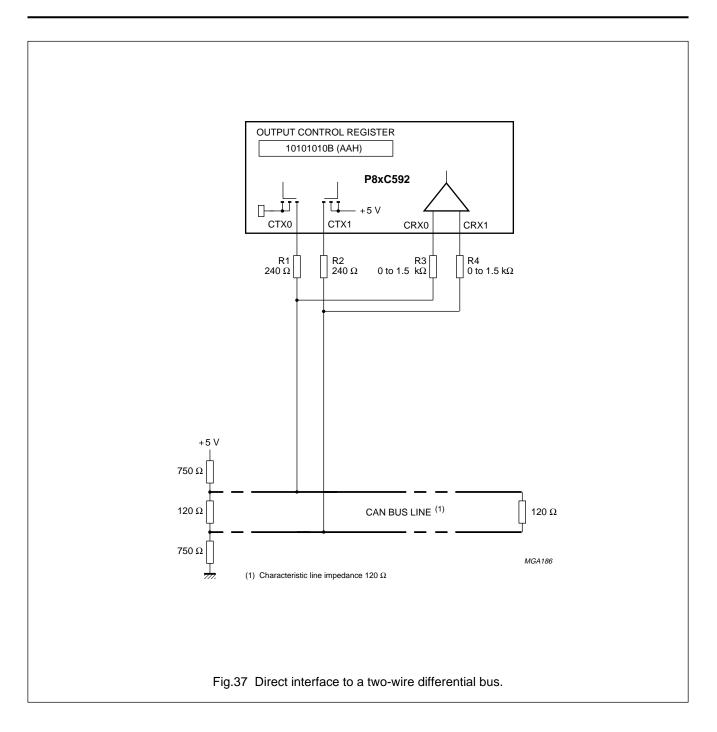

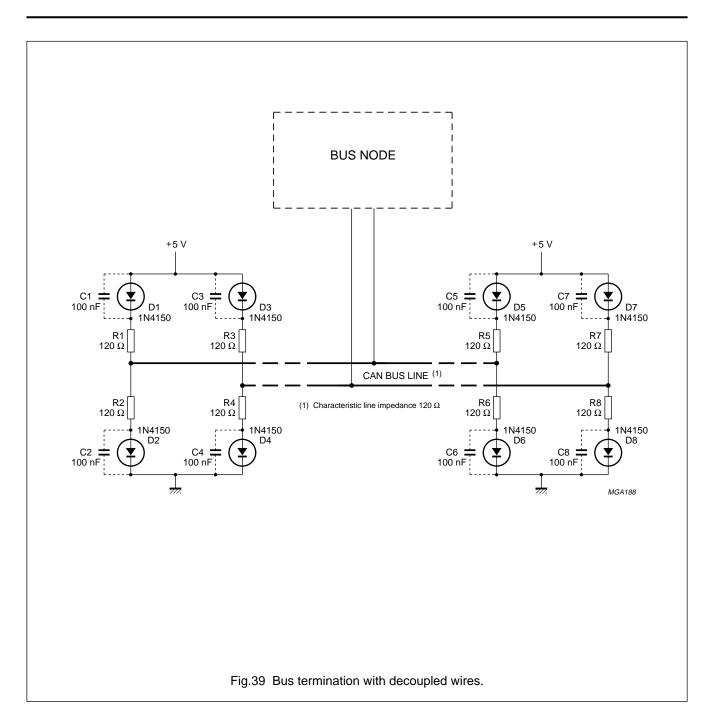

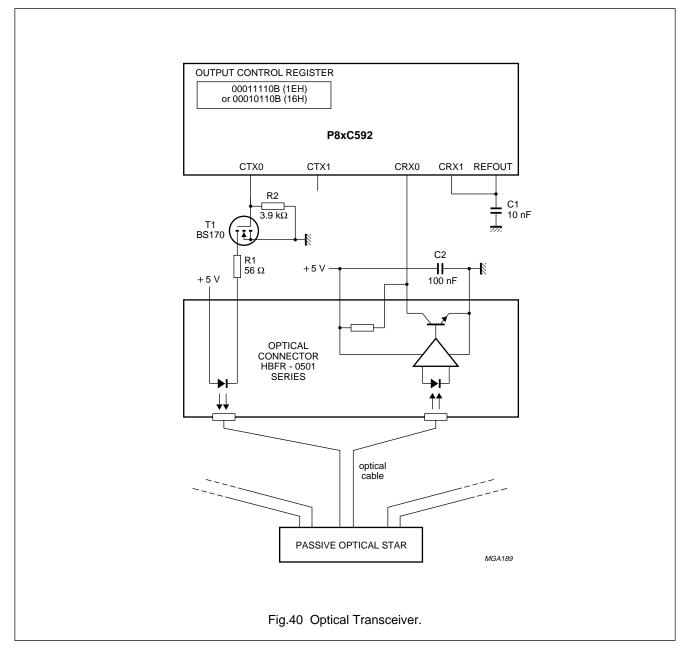

The P8xC592 CAN-controller contains all necessary hardware for high performance serial network communications (see Fig.14 and Table 29).

It controls the communication flow through the area network using the CAN-protocol. The CAN-controller meets the following automotive requirements:

- Short message length

- Bus access priority, determined by the message identifier

- Powerful error handling capability

- Configuration flexibility to allow area network expansion

- · Guaranteed latency time for urgent messages;

- The latency time defines the period between the initiation (Transmission Request) and the start of the transmission on the bus. The latency time strongly depends on a large variety of bus-related conditions. In the case of a message being transmitted on the bus and one distortion, the latency time can be up to 149 bit times (worst case). For more information see Chapter 22 "CAN application information".

## P8xC592

#### Table 29 Hardware blocks of the CAN-controller (see Fig.14)

| NAME                       | BLOCK | DESCRIPTION                                                                                                                                                 |

|----------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface Management Logic | IML   | Interprets commands from the CPU, allocates the message buffers (TBF, RBF0 and RBF1) and provides interrupts and status information to the microcontroller. |

| Transmit Buffer            | TBF   | 10 bytes memory into which the CPU writes messages which are to be transmitted over the CAN network.                                                        |

| Receive Buffers (0 and 1)  | RBF0  | RBF0 and RBF1 are each 10 bytes memories which are alternatively used to                                                                                    |

|                            | RBF1  | store messages received from the CAN network.<br>The CPU can process one message while another is being received.                                           |

| Bit Stream Processor       | BSP   | Is a sequencer, controlling the data stream between the Transmit Buffer,<br>Receive Buffers (parallel data) and the CAN-bus (serial data).                  |

| Bit Timing Logic           | BTL   | Synchronizes the CAN-controller to the bitstream on the CAN-bus.                                                                                            |

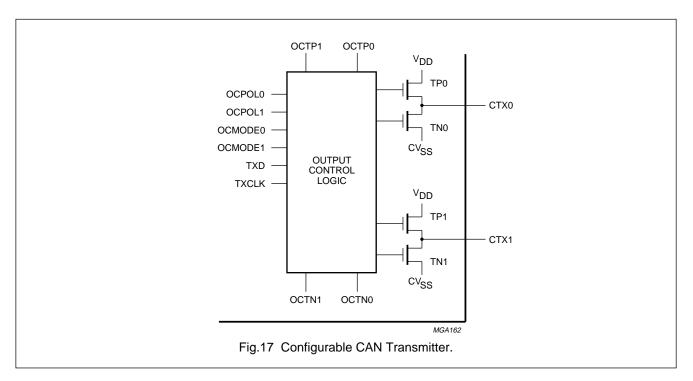

| Transceiver Control Logic  | TCL   | Controls the output driver.                                                                                                                                 |

| Error Management Logic     | EML   | Performs the error confinement according to the CAN-protocol.                                                                                               |

# 13.5 Control Segment and Message Buffer description

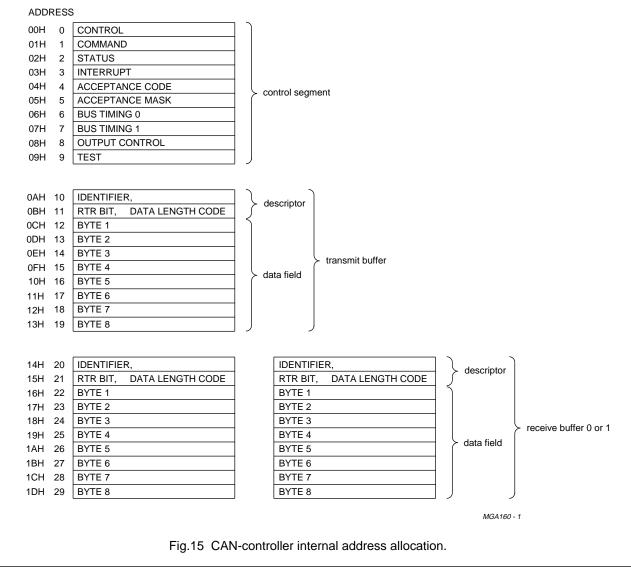

The CAN-controller appears to the CPU as a memory-mapped peripheral, guaranteeing the independent operation of both parts.

#### 13.5.1 ADDRESS ALLOCATION

The address area of the CAN-controller consists of the Control Segment and the message buffers. The Control Segment is programmed during an initialization down-load in order to configure communication parameters (e.g. bit timing). The communication over the CAN-bus is also controlled via this segment by the CPU. A message which is to be transmitted, must be written to the Transmit Buffer. After a successful reception the CPU may read the message from the Receive Buffer and then release it for further use.

#### 13.5.2 CONTROL SEGMENT LAYOUT

The exchange of status, control and command signals between the CPU and the CAN-controller is performed in the control segment. The layout of this segment is shown in Fig.15. After an initial down-load, the contents of the registers Acceptance Code, Acceptance Mask, Bus Timing 0, Bus Timing 1 and Output Control should not be changed. These registers may only be accessed when the Reset Request bit in the Control Register is set HIGH (see Tables 30, 31 and 32).

| Table 30 | CPU/CAN Register map |

|----------|----------------------|

|----------|----------------------|

|               | BIT            |                          |                               |                          |                        |                          |                        |  |  |  |

|---------------|----------------|--------------------------|-------------------------------|--------------------------|------------------------|--------------------------|------------------------|--|--|--|

| 7             | 6              | 5                        | 4                             | 3                        | 2                      | 1                        | 0                      |  |  |  |

| Control Seg   | ment           |                          |                               |                          | ł                      | •                        |                        |  |  |  |

| ADDRESS 0: C  | ONTROL REGIS   | TER                      |                               |                          |                        |                          |                        |  |  |  |

| ТМ            | S              | RA                       | OIE                           | EIE                      | TIE                    | RIE                      | RR                     |  |  |  |

| ADDRESS 1: C  | COMMAND REGIS  | STER                     |                               |                          |                        |                          |                        |  |  |  |

| RX0A          | RX1A           | WUM                      | SLP                           | COS                      | RRB                    | AT                       | TR                     |  |  |  |

| ADDRESS 2: S  | TATUS REGISTE  | R                        |                               |                          |                        |                          | •                      |  |  |  |

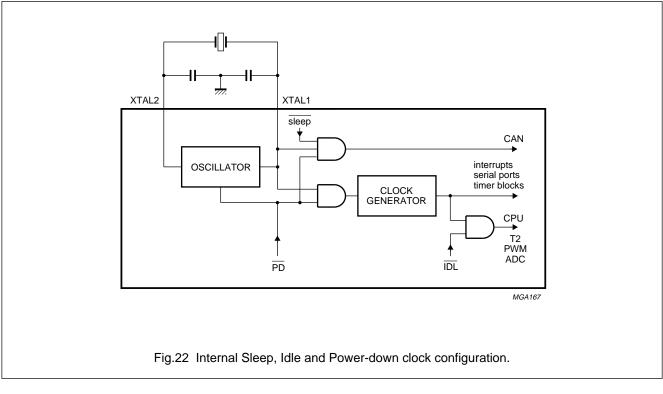

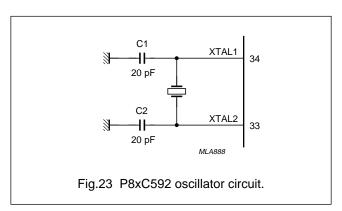

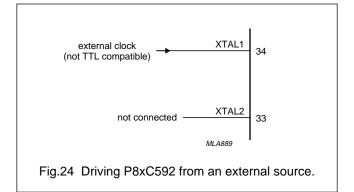

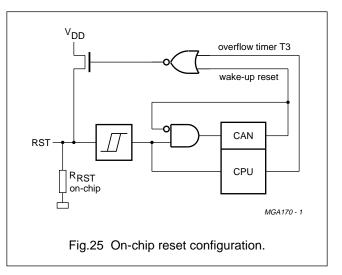

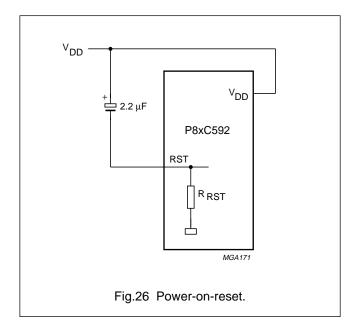

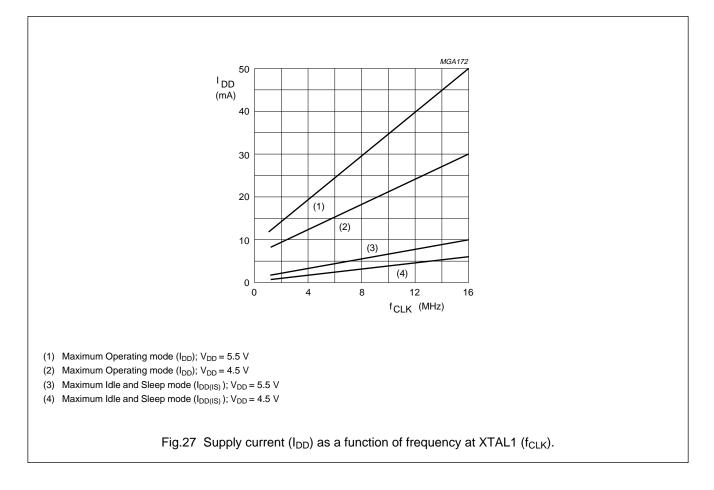

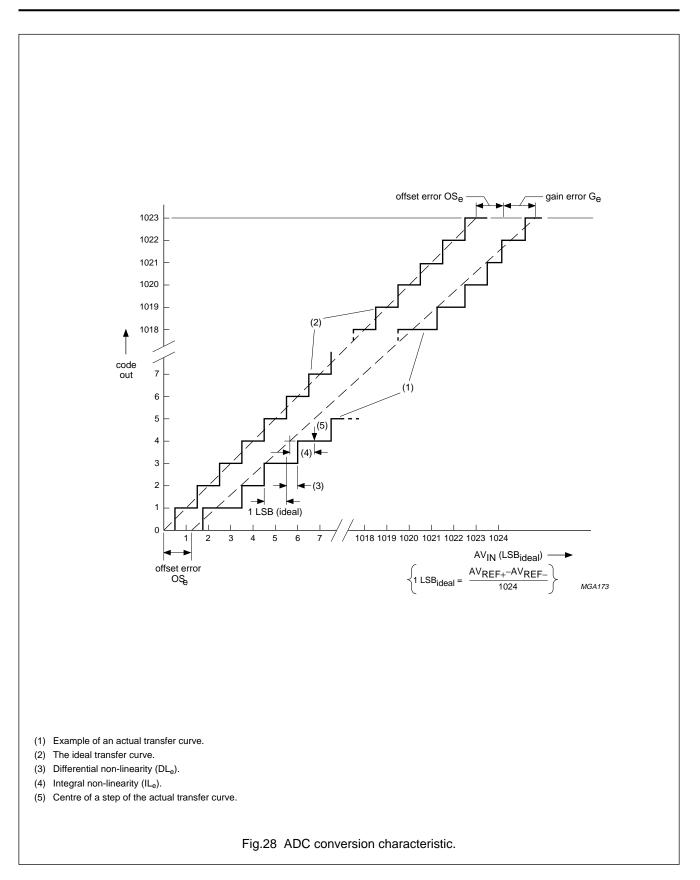

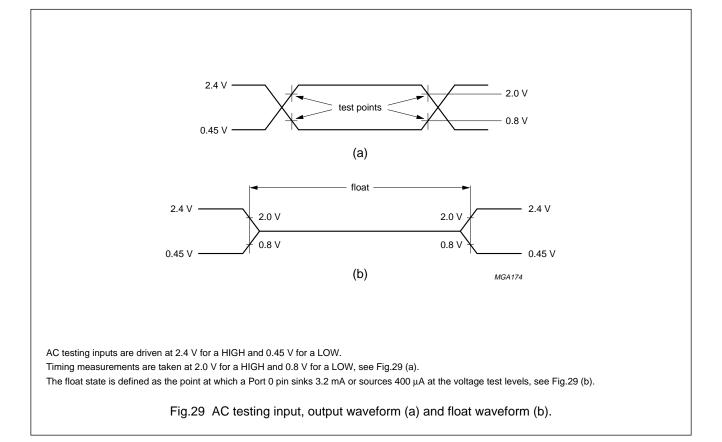

| BS            | ES             | TS                       | RS                            | TCS                      | TBS                    | DO                       | RBS                    |  |  |  |